طراحی مدارهای بایاس ترانزیستور؛ الکترونیک 1؛ فصل 6؛ بخش دوم

- مهندسی برق, الکترونیک

- سعید زوارقی

- 2 دقیقه

سلام و عرض ادب خدمت دوستان عزیزم؛ مبحث امروز ما ادامه جلسه قبل از فصل 6 ام هست که در مورد طراحی مدارهای بایاس ترانزیستور هست. همراهی شما تا انتهای مطلب باعث دلگرمی ما خواهد بود.

چرا ترجیح میدیم همیشه ترانزیستور در ناحیه فعال باشد؟

در مدار قبل در صورتیکه بخواهیم جریان کلکتور بیشترین دامنه ی تغییرات را در دو طرف نقطه ی کار داشته باشد باید حتی الامکان نقطه ی کار Q را در وسط خط بار DC انتخاب کنیم. در صورتیکه نقطه ی کار را نزدیک ناحیه ی اشباع (نقطه ی ) A یا نزدیک ناحیه ی قطع (نقطه ی ) B انتخاب کنیم با تغییرات کوچک دما جریان کلکتور تغییر کرده و ترانزیستور به ناحیه ی اشباع یا قطع رفته و از ناحیه ی خطی خارج می شود. یعنی اگر ترانزیستور در ناحیه اشباع یا قطع باشد با افزایش یا کاهش جزئی دما در ترانزیستور جریان کلکتور به مقدار قابل ملاحظهای تغییر میکند که مطلوب نیست.

بایاس مدار امیتر مشترک و جلوگیری از رانش حرارتی

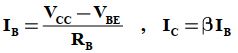

یکی از مشکلاتی که مدار قبل دارد این است که از دو منبع DC مختلف ( VCC ,VBB) در بایاس مدار استفاده شده است که به لحاظ پیاده سازی اصلا صحیح نیست. برای حل این مشکل از مدار رو به رو استفاده می شود. در این مدار از یک منبع استفاده شده است و داریم:

مدار رو به رو دو عیب اساسی دارد:

- جریان کلکتور به وابسته است و چون مقدار دقیق مشخص نیست و از طرفی مقدار برای ترانزیستورهای مشابه ممکن است متفاوت باشد طراحی

نقطه ی کار با مشکل مواجه می شود.

- در صورتیکه دمای محیط افزایش یابد جریان کلکتور نیز افزایش می یابد. دقت کنید که این افزایش دما به خاطر وابستگی شدید VCBO به دما است. با افزایش IC ترانزیستور گرمتر شده و در نتیجه دوباره IC افزایش می یابد و این روند به همین صورت ادامه پیدا می کند و منجر به خارج شدن ترانزیستور از ناحیه ی فعال می شود. اصطلاحا در این حالت ترانزیستور در وضعیت رانش حرارتی قرار گرفته است.

برای جلوگیری از رانش حرارتی ترانزیستور مدار رو به رو پیشنهاد شد.

![]()

در مدار رو به رو در صورت افزایش دما IC افزایش می یابد. افزایش IC کاهش VC را به دنبال دارد. کاهش VC باعث کاهش IB می شود (VBE تقریبا ثابت است) و کاهش IB کاهش IC را به دنبال دارد. بنابراین IC کنترل می شود.

در این مدار مشکل وابستگی IC به β حل نشده است. برای حل هر دو شکل مدار زیر که به مدار خود بایاس (self bias) معروف است پیشنهاد می شود که در جلسه بعدی مفصلا بحث خواهیم کرد.

این هم از جلسه امروز و پایان جلسه اول. توی جزوه سعی کردیم با مثال های بیشتر این جلسه را برایتان کامل تشریح کنیم. در قالب آموزش ویدئویی هم با جزئیات کامل مطالب توضیح داده شد.

سپاسگزاریم که این جلسه نیز ما را همراهی کردید.

موفق و پیروز باشید.